PLL Upgrade for DB6NT MK2 13cm Transverter

2 minute read

June 2016

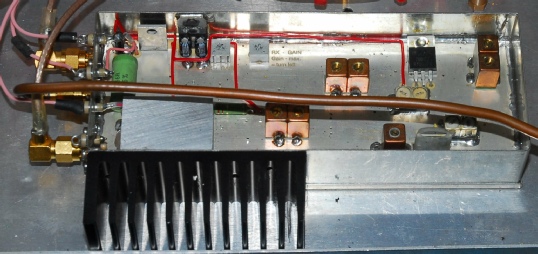

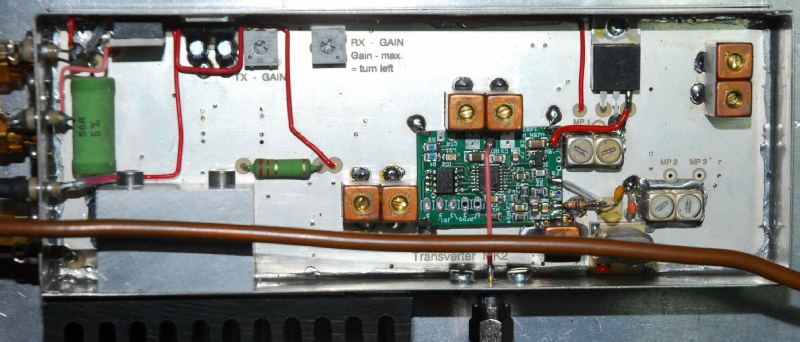

It is ten years since I built my MK2 13cm transverter (above). Back then the concept of phase-locking the local oscillator of such things was a relatively major project and to be honest, I wasn’t too worried about frequency accuracy since I had a couple of ways of verifying and compensating for any offset. A few months ago, a friend of mine purchased two of OZ5N’s ‘Auto-PLL’ kits … one for his 13cm transverter and the other for his 9cm transverter. Due to an oversight on his part, he had forgotten that his 9cm transverter is in fact a G3 DB6NT design and thus has LO PLL locking built in. As a result he passed the extra kit on to myself.

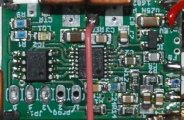

Wow! How technology has advanced. No offence to CT1DMK and VE1ALQ who developed the CPLD board on the left. This is the PLL board used to lock the LO in my 9cm transverter to my 10MHz GPSDO. The board, dated 2007, is roughly 6cm square and continues to give me good service.

Steen Nielsen, OZ5N’s Auto-PLL board, on the right is a real advancement in technology. The principle is identical, however advances in technology have simplified the implementation such that the PCB measures a mere 2cm x 3cm.

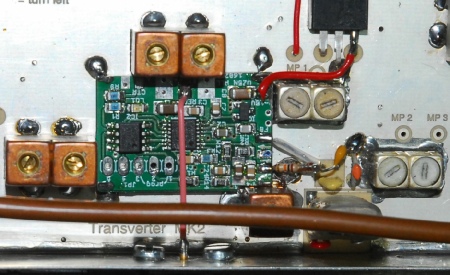

It is probably a safe bet that the board was designed with the layout of the 13cm transverter in mind! Again, no disrespect to CT1DMK and VE1ALQ; what distinguishes this design is the fact that initial configuration is completely automatic and it can handle a wide range of Local Oscillator frequencies without the need for any preset links.

The heart of the design is a PIC12F1840 8-bit microcontroller crammed into an 8-pin package, in this case SOIC (surface mount). The actual PLL component is an Analog Devices ADF4002. When configuration is initiated, the microcontroller measures the frequency of both the reference and the local oscillator. It then calculates the two divisors such that the resulting quotients are theoretically identical. These divisors are used to preset the reference and N-dividers in the ADF4002 and the resulting output is used to tune the transverter crystal oscillator by way of a (supplied) varicap diode. A minimum amount of modification to the original transverter is required. The hardest part was fitting the SMA connector (not part of the kit) for the 10MHz reference.

The heart of the design is a PIC12F1840 8-bit microcontroller crammed into an 8-pin package, in this case SOIC (surface mount). The actual PLL component is an Analog Devices ADF4002. When configuration is initiated, the microcontroller measures the frequency of both the reference and the local oscillator. It then calculates the two divisors such that the resulting quotients are theoretically identical. These divisors are used to preset the reference and N-dividers in the ADF4002 and the resulting output is used to tune the transverter crystal oscillator by way of a (supplied) varicap diode. A minimum amount of modification to the original transverter is required. The hardest part was fitting the SMA connector (not part of the kit) for the 10MHz reference.

Once lock is achieved for the first time, the settings are automatically stored in the CPU … thereafter, lock is obtained almost instantly as long as the GPSDO reference is locked.

More information (price etc.) on the OZ5N Auto-PLL can be found here.